Introduction

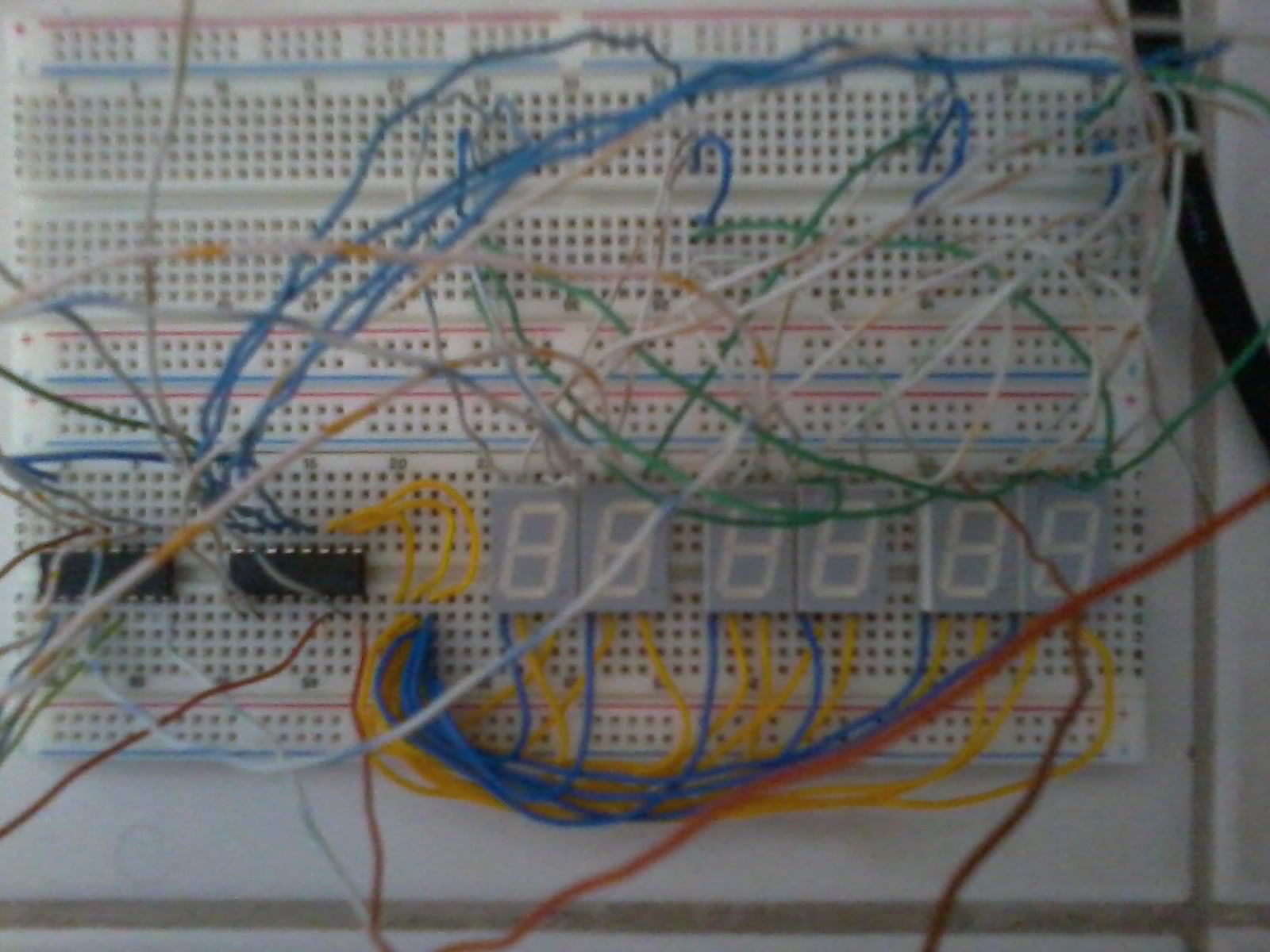

This article is about controlling 7-segment displays in real time via parallel port and x86 assembly. Project contains SN74LS57N decoder/driver, 74HC238 demultiplexer/driver and 6 Seven-segment displays. I will show how to multiplexing between 6 Seven-segment displays with a single decoder/driver.

http://youtu.be/kwiHF2zoIpI

The materials needed

- SN74LS47N BCD to 7-segment display decoder. (for anode displays)

- 74HC238 3 to 8 demultiplexer

- 6 x anode 7-Segment display

- Breadboard

- About 5 meter cable

1.What is the Multiplexing and Demultiplexing ?

Multiplexing, a source, shared among many users that use it. The multiplexed signal is transmitted over a communication channel, which may be a physical transmission medium. The multiplexing divides the capacity of the high-level communication channel into several low-level logical channels, one for each message signal or data stream to be transferred. A reverse process, known as demultiplexing, can extract the original channels on the receiver side. A device that performs the multiplexing is called a multiplexer (MUX), and a device that performs the reverse process is called a demultiplexer (DEMUX). Inverse multiplexing (IMUX) has the opposite aim as multiplexing, namely to break one data stream into several streams, transfer them simultaneously over several communication channels, and recreate the original data stream. There is 4 type space-division multiplexing (SDM), frequency-division multiplexing (FDM), time-division multiplexing (TDM), and code division multiplexing (CDM).

1.1 What is the Time-Division Multiplexing ?

Time-division multiplexing (TDM) is a type of digital (or rarely analog) multiplexing in which two or more bit streams or signals are transferred apparently simultaneously as sub-channels in one communication channel, but are physically taking turns on the channel.

1.2 Time-Division Multiplexing in this Project

TDM simply we can say sharing the resource each part in equal time.

Figure1

Figure2

Each line should selected very quickly. If duration of each group 1 sec instead of 1/1000 sec (1 khz) system will show like Figure 3.

Figure3

The human brain can not detect this fast switching operation. There is several advantages of this method. Most important advantages is using just single source. In this project I shared SN74LS47N decoder between parallel connected 6 x Seven-Segment displays.

2.Seven-Segment Displays

7-Segment display is kind of binary to decimal converter. There is two types of displays. Common anode and common cathode.

Main difference between common anode and common cathode 7-segment.

Truth Table of 7-Segment Displays

3.SN74LS47N BCD to Seven-Segmen Decoder/Driver

SN74LS47N Decoder/Driver uses for anode displays. There is 4 bit bcd input and 7 display output. The SN74LS47 are Low Power Schottky BCD to 7-Segment Decoder/Drivers consisting of NAND gates, input buffers and seven AND-OR-INVERT gates. They offer active LOW, high sink current outputs for driving indicators directly. Seven NAND gates and one driver are connected in pairs to make BCD data and its complement available to the seven decoding AND-OR-INVERT gates. The remaining NAND gate and three input buffers provide lamp test, blanking input / ripple-blanking output and ripple-blanking input. The circuits accept 4-bit binary-coded decimal (BCD) and, depending on the state of the auxiliary inputs, decodes this data to drive a 7-segment display indicator. The relative positive-logic output levels, as well as conditions required at the auxiliary inputs, are shown in the truth tables. Output configurations of the SN74LS47 are designed to withstand the relatively high voltage required for 7-segment indicators. These outputs will withstand 15 V with a maximum reverse current of 250 mA. Indicator segments requiring up to 24 mA of current may be driven directly from the SN74LS47 high performance output transistors. Display patterns for BCD input counts above nine are unique symbols to authenticate input conditions.

Pin Diagram of SN74LS47N

Pin Description of SN74LS47N

Truth Table of SN74LS47N

4. 74HC238 3 to 8 line Decoder/Demultiplexer

The 74HC/HCT238

are high-speed Si-gate CMOS devices and are pin compatible with low power

Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no.

7A. The 74HC/HCT238 decoders accept three binary weighted address inputs (A0,

A1, A2) and when enabled, provide 8 mutually exclusive active HIGH outputs (Y0

to Y7). The “238” features three enable inputs: two active LOW (E1 and E2) and

one active HIGH (E3). Every output will be LOW unless E1 and E2 are LOW and E3

is HIGH. This multiple enable function allows easy parallel expansion of the

“238” to a 1-of-32 (5 lines to 32 lines) decoder with just four “238” ICs and

one inverter. The “238” can be used as an eight output demultiplexer by using

one of the active LOW enable inputs as the data input and the remaining enable

inputs as strobes. Unused enable inputs must be permanently tied to their

appropriate active HIGH or LOW state. The “238” is identical to the “138” but

has non-inverting outputs.

Pin Diagram of 74HC238

Pin Description of 74HC238

Truth Table of 74HC238

5.Parallel Port (LPT Port)

Parallel pots are

personal computer interfaces that transfer data (generally) a byte at a time. Parallel

ports conform to the specifications of a document of the Institute of

Electrical and Electronic Engineers (IEEE) called IEEE Std 1284-1994: Standard

Signaling. Method for a Bi-directional Parallel Peripheral Interface for

Personal Computers, or IEEE 1284 for short. Basically,

IEEE-1284 gathers and harmonizes standards for parallel transmission that were

already in use. It describes a system of asynchronous, fully interlocked,

bi-directional communications between a peripheral (often a printer) and host

(usually a PC).

The IEEE 1284

parallel port modes are called

Compatibility

mode,

Nibble mode,

Byte mode,

Enhanced mode,

Enhanced Parallel Port (EPP),

Extended Cağabilities Port (ECP)

Pin Diagram of Parallel Port

Pin Description of Parallel Port

Standart Parallel Port Addresses

IEEE 1284 level II

Data output

(>2.4V) 14 mA

Data line sink

(<0.4V) 14

mA

Control output

(>2.4 V) ?

Signal lines

(short circuit) ?

Control line

sink (<0.4V) 14 mA

6.Designing Circuit

Basic part of the

project design the circuit. I decided to use just 8 data register from LPT

port.

All seven segment

displays are connected parallel each other. First 4 bit (pin 2 to 5) from

parallel port reserved for SN74LS47N data inputs. This means shown digit is determined here. Next 3 bit (pin 6 to

8) from parallel port reserved for 74HC238 switching input. Last bit (pin 9)

used for Vcc inputs of the system.

| Decimal

128-255

| D7 Vcc

| D6,D5,D4

74238 BCD

| D3,D2,D1,D0

7447 BCD

| Selected

Display

| Displayed

Number

|

| 129

| 1

| 000

| 0001

| 1

| 1

|

| 144

| 1

| 001

| 0000

| 2

| 0

|

| 160

| 1

| 010

| 0000

| 3

| 0

|

| 176

| 1

| 011

| 0000

| 4

| 0

|

| 192

| 1

| 100

| 0000

| 5

| 0

|

| 208

| 1

| 101

| 0000

| 6

| 0

|

| 130

| 1

| 000

| 0010

| 1

| 2

|

| 144

| 1

| 001

| 0000

| 2

| 0

|

| 160

| 1

| 010

| 0000

| 3

| 0

|

| 176

| 1

| 011

| 0000

| 4

| 0

|

| 192

| 1

| 100

| 0000

| 5

| 0

|

| 208

| 1

| 101

| 0000

| 6

| 0

|

Some Part of System's Truth Table

SEG1 SEG2 SEG3 SEG4 SEG5 SEG6

128 0 144 0

160 0 176 0

192 0 208 0

129 1 145 1 161 1 177 1 193 1 209 1

130 2 146 2 162 2 178 2 194 2 210 2

131 3 147 3 163 3 179 3 195 3 211 3

132 4 148 4

164 4 180 4 196 4 212 4

133 5 149 5 165 5 181 5 197 5 213 5

134 6 150 6 166 6 182 6 198 6 214 6

135 7 151 7 167 7 183 7 199 7 215 7

136 8 152 8 168 8 184 8 200 8 216 8

137 9 153 9 169 9 185 9

201 9 217 9

+7 Don’t Care

7. How to Programming in x86 Assembly ?

mov cx,0ffffh

loop1:

mov dx,03bch

MOV al,10000000b

out dx,al

dec cx

jnz loop1

This code block send the (128d) 10000000b logic high and low voltage respectively

d7,d6,d5,d4,d3,d2,d1,d0 pins and loop show digit during about 1 second 800Mhz processor high priority on windows xp operating system. During time exactly can’t

calculated for different systems. Refresh rate and streaming rate will never be able to

stable on different machines. Modern Real time operating systems shares the

resources with many threats. if I used the pick controller on this project it can be calculated

exacly.

MOV bl,127d

mov cx,10d

next:

push cx

INC bl

mov cx,5d

duration:

push cx

mov cx,0500h

loop1:

mov dx,03bch

MOV al,bl

out dx,al

dec cx

jnz loop1

mov cx,0500h

loop2:

mov dx,03bch

MOV al,144d

out dx,al

dec cx

jnz loop2

mov cx,0500h

loop3:

mov dx,03bch

MOV al,160d

out dx,al

dec cx

jnz loop3

mov cx,0500h

loop4:

mov dx,03bch

MOV al,176d

out dx,al

dec cx

jnz loop4

mov cx,0500h

loop5:

mov dx,03bch

MOV al,192d

out dx,al

dec cx

jnz loop5

mov cx,0500h

loop6:

mov dx,03bch

MOV al,208d

out dx,al

dec cx

jnz loop6

pop cx

loop duration

pop cx

loop next

8. References

- SN74LS47N semiconductor datasheet

- 74HC238 philips datasheet

- IEEE 1284 STD

9. Contact

http://blog.armanasci.com